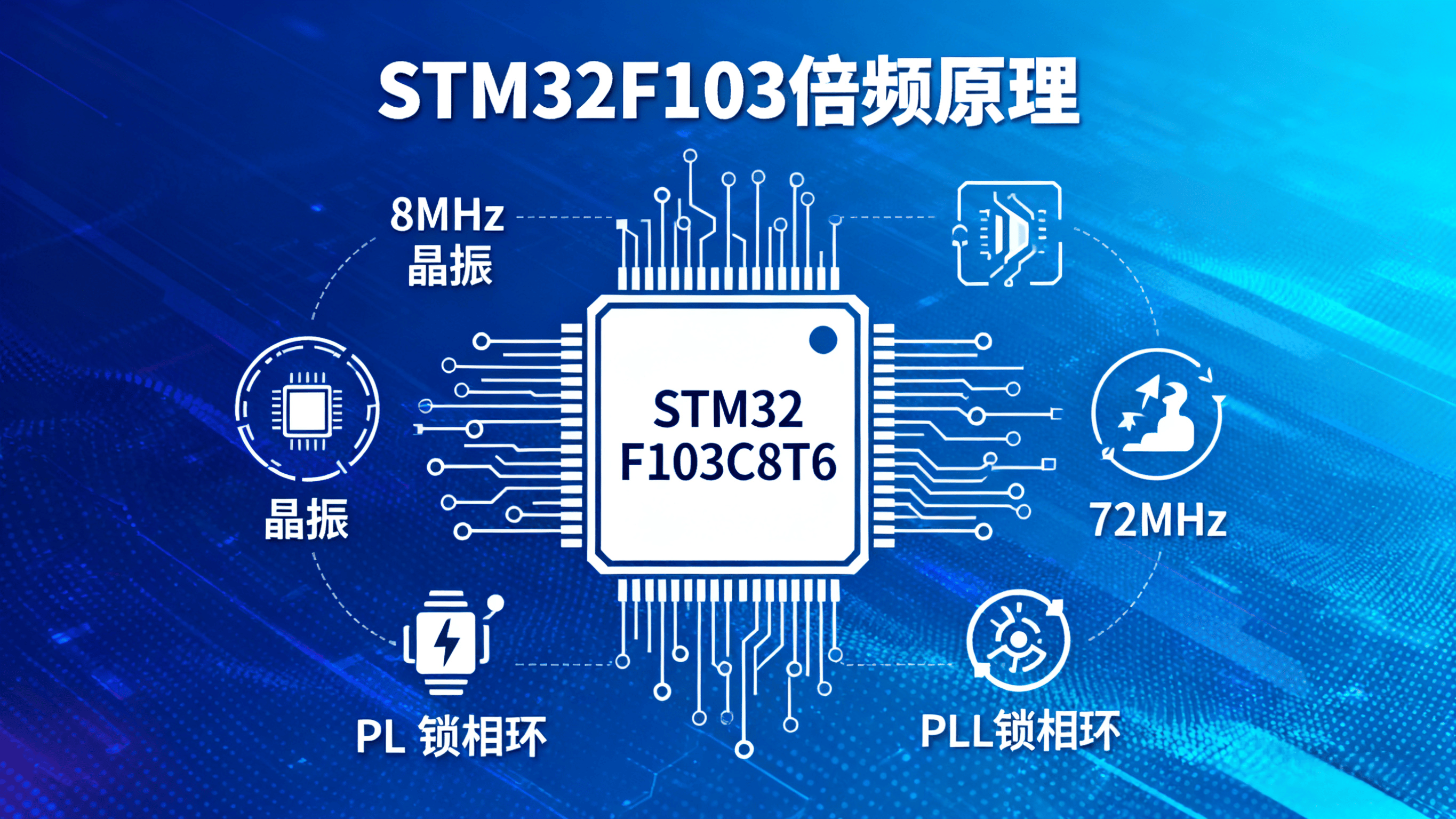

一、锁相环(PLL)的倍频原理

二、STM32F103 的时钟树倍频流程

1. 选择时钟源:HSE 作为 PLL 输入

2. 配置 PLL 倍频系数

3. 使能 PLL 并切换系统时钟

三、实际代码配置示例(标准库 / 寄存器级)

#include "stm32f10x.h"

void SystemClock_Config(void) {

// 1. 使能外部晶振(HSE)

RCC->CR |= RCC_CR_HSEON; // 开启 HSE

while (!(RCC->CR & RCC_CR_HSERDY)); // 等待 HSE 稳定

// 2. 配置 PLL:选择 HSE 为源,9 倍频

RCC->CFGR |= RCC_CFGR_PLLSRC; // PLL 时钟源 = HSE(不分频)

RCC->CFGR |= RCC_CFGR_PLLMULL9; // 9 倍频 → 8MHz × 9 = 72MHz

RCC->CR |= RCC_CR_PLLON; // 使能 PLL

while (!(RCC->CR & RCC_CR_PLLRDY)); // 等待 PLL 稳定

// 3. 切换系统时钟为 PLL 输出

RCC->CFGR &= ~RCC_CFGR_SW; // 清除原时钟源配置

RCC->CFGR |= RCC_CFGR_SW_PLL; // 系统时钟 = PLL 输出

while ((RCC->CFGR & RCC_CFGR_SWS) != RCC_CFGR_SWS_PLL); // 等待切换完成

// 4. 配置总线时钟(可选):HCLK = SYSCLK,PCLK2 = HCLK,PCLK1 = HCLK/2

RCC->CFGR |= RCC_CFGR_HPRE_DIV1; // HCLK = SYSCLK(72MHz)

RCC->CFGR |= RCC_CFGR_PPRE2_DIV1; // PCLK2 = HCLK(72MHz,APB2 总线)

RCC->CFGR |= RCC_CFGR_PPRE1_DIV2; // PCLK1 = HCLK/2(36MHz,APB1 总线)

}

四、倍频的 “灵活性” 与 “限制”

总结

声明:本站所有文章,如无特殊说明或标注,均为本站原创发布。任何个人或组织,在未征得本站同意时,禁止复制、盗用、采集、发布本站内容到任何网站、书籍等各类媒体平台。如若本站内容侵犯了原著者的合法权益,可联系我们进行处理。